# HITACHI PROGRAMMABLE CONTROLLER

# HIDICEH-150

# **Counter Module EH-CU/CUE**

**APPLICATION MANUAL**

NJI-321B(X)

# **Revision History**

| No. | Description of Revision                                                                                                                                     | Data of   | Manual<br>Number |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|

| 1   | First edition                                                                                                                                               |           | NJI-321(X)       |

| 2   | Count value record mode addition<br>(P1-2, P3-3, P7-5, P7-12, P7-13, Appendix A2)<br>Error correction<br>(P1-2, P5-1, P702, P7-3, P7-14)<br>EH-CUE addition | 2001/10/1 | NJI-321A(X)      |

| 3   | Differential voltage added.                                                                                                                                 | 2004/8    | NJI-321B(X)      |

### Safety Precautions

Read this manual and related documents thoroughly before installing, operating, performing preventive maintenance or performing inspection, and be sure to use the unit correctly. Use this product after acquiring adequate knowledge of the unit, all safety information, and all cautionary information. Also, make sure this manual enters the possession of the chief person in charge of safety maintenance.

Safety caution items are classified as "Danger" and "Caution" in this document.

: Cases where if handled incorrectly a dangerous circumstance may be created, resulting in possible death or severe injury.

: Cases where if handled incorrectly a dangerous circumstance may be created, resulting in possible minor to medium injury to the body, or only mechanical damage.

However, depending on the circumstances, items marked with

CAUTION may result in major accidents.

is

In any case, they both contain important information, so please follow them closely.

Icons for prohibited items and required items are shown below:

S : Indicates prohibited items (items that may not be performed). For example, when open flames are prohibited, is shown.

: Indicates required items (items that must be performed). For example, when grounding must be performed,

shown.

#### 1. About installation

#### 2. About wiring

# REQUIRED

• Always perform grounding (FE terminal).

If grounding is not performed, there is a risk of electric shocks and malfunctions.

# **A**CAUTION

- Connect power supply that meets rating. If a power supply that does not meet rating is connected, fire may be caused.

- The wiring operation should be performed by a qualified personnel. If wiring is performed incorrectly, it may result in fire, damage, or electric shock.

#### 3. Precautions when using the unit

# DANGER

• Do not touch the terminals while the power is on. There is risk of electric shock.

• Structure the emergency stop circuit, interlock circuit, etc. outside the programmable controller (hereinafter referred to as PC).

Damage to the equipment or accidents may occur due to failure of the PC.

However, do not interlock the unit to external load via relay drive power supply of the relay output module.

# **A**CAUTION

- When performing program change, forced output, RUN, STOP, etc., while the unit is running, be sure to verify safety. Damage to the equipment or accidents may occur due to operation error.

- Supply power according to the power-up order. Damage to the equipment or accidents may occur due to malfunctions.

#### 4. About preventive maintenance

## DANGER

• Do not connect the (+), (-) of the battery in reverse. Also, do not charge, disassemble, heat, place in fire, or short circuit the battery.

There is a risk of explosion or fire.

#

• Do not disassemble or modify the unit. These actions may result in fire, malfunction, or malfunction.

# **A**CAUTION

• Turn off the power supply before removing or attaching module/unit. Electric shock, malfunction or failure may result.

#### WARNING

To ensure that the equipment described by this manual. As well as all equipment connected to and used with it, operate satisfactorily and safety, all applicable local and national codes that apply to installing and operating the equipment must be followed. Since codes can vary geographically and can change with time, it is the user's responsibility to determine which standard and codes apply, and to comply with them.

FAILURE TO COMPLY WITH APPLICABLE CODES AND STANDARDS CAN RESULT IN DAMAGE TO EQUIPMENT AND/OR SERIOUS INJURY TO PERSONNEL.

INSTALL EMARGENCY POWER STOP SWITCH, WHICH OPERATES INDEPENDENTLY OF THE PROGRAMMABLE CONTROLLER TO PROTECT THE EQUIPMENT AND/OR PERSONNEL IN CASE OF THE CONTROLLER MALFUNCTION.

Personnel who are to install and operate the equipment should carefully study this manual and any other referred to by it prior to installation and/or operation of the equipment. Hitachi Industrial Equipment Systems Co., Ltd. constantly strives to improve its products, and the equipment and the manual(s) that describe it may be different from those already in your possession.

If you have any questions regarding the installation and operation of the equipment, or if more information is desired, contact your local Authorized Distributor or Hitachi Industrial Equipment Systems Co., Ltd.

### IMPORTANT

THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND, IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTION MANUAL, MAY CAUSE INTERFERENCE TO RADIO COMMUNICATIONS. AS TEMPORARILY PERMITTED BY REGULATION, IT HAS NOT BEEN TESTED FOR COMPLIANCE WITH THE LIMITS FOR CLASS A COMPUTING DEVICES PURSUANT TO SUBPART J OF PART 15 OF FCC ROULES, WHICH ARE DESIGNED TO PROVIDE PEASONABLE PROTECTION AGAINST SUCH INTERFERENCE.

OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES MAY BE REQUIRED TO CORRECT THE INTERFERENCE.

### LIMITED WARRANTY AND IMITATION OF LIABILITY

Hitachi Industrial Equipment Systems Co., Ltd. (Hitachi) warrants to the original purchaser that the programmable logic controller (PLC) manufactured by Hitachi is free from defects in material and workmanship under normal use and service. The obligation of Hitachi under this warranty shall be limited to the repair or exchange of any part or parts which may prove defective under normal use and service within eighteen (18) months from the date of manufacture or twelve (12) months from the date of installation by the original purchaser which ever occurs first, such defect to be disclosed to the satisfaction of Hitachi after examination by Hitachi of the allegedly defective part or parts. This warranty in expressly in lieu of all other warranties expressed or implied including the warranties of merchantability and fitness for use and of all other obligations or liabilities and Hitachi neither assumes, nor authorizes any other person to assume for Hitachi, any other liability in connection with the sale of this PLC. This warranty shall not apply to this PLC or any part hereof which has been subject to accident, negligence, alternation, abuse, or misuse. Hitachi makes no warranty whatsoever in respect to accessories or parts not supplied by Hitachi. The term "original purchaser", as used in this warranty, shall be deemed to mean that person for whom the PLC in originally installed.

In no event, whether as a result of breach of contract, warranty, tort (including negligence) or otherwise, shall Hitachi or its suppliers be liable for any special, consequential, incidental or penal damages including but not limited to, loss or profit or revenues, loss of use of the products or any associated equipment, damage to associated equipment, cost of capital, cost of substitute products, facilities, services or replacement power, down time costs, or claims of original purchaser's customers for such damages.

To obtain warranty service, return the product to your distributor, or send it with a description of the problem, proof of purchase, post paid, insured, and in a suitable package to:

Quality Assurance Dept. Hitachi Industrial Equipment Systems Co., Ltd. 46-1 Ooaza-Tomioka Nakajo-machi Kitakanbara-gun, Niigata-ken 959-2608 JAPAN

#### Copyright 2002 by Hitachi Industrial Equipment Systems Co., Ltd. All Right Reserved – Printed in Japan

The Information and/or drawing set forth in this document and all right in and to inventions disclosed herein and patent which might be granted thereon disclosing or employing and the materials, methods, techniques or apparatus described herein are the exclusive property of Hitachi Industrial Equipment Systems Co., Ltd.

No copies of the information or drawings shall be made without the prior constant of Hitachi Industrial Equipment Systems Co., Ltd.

Hitachi Industrial Equipment Systems Co., Ltd. provides customer assistance in varied technical areas. Since Hitachi does not possess full access to data concerning all of the uses and applications of customer's products, responsibility is assumed by Hitachi neither for customer product design nor for any infringement of patents or rights of others, which may result from Hitachi assistance.

The specifications and descriptions contained in this manual were accurate at the time they were approved for printing. Since Hitachi Industrial Equipment Systems Co., Ltd. Incorporated constantly strives to improve all its products, we reserve the right to make changes to equipment and/or manual at any time without notice and without incurring any obligation other than as noted in this manual.

Hitachi Industrial Equipment Systems Co., Ltd. assumes no responsibility for errors that may appear in this manual.

As the product works with user program, and Hitachi Industrial Equipment Systems Co., Ltd. cannot test all combination of user program components, it is assumed that a bug or bugs may happen unintentionally. If it is happened: please inform the fact to Hitachi Industrial Equipment Systems Co., Ltd. or its representative. Hitachi will try to find the reason as much as possible and inform the countermeasure when obtained.

Nevertheless Hitachi Industrial Equipment Systems Co., Ltd. intends to make products with enough reliability, the product has possibility to be damaged at any time. Therefore personnel who are to install and operate the equipment have to prepare with the countermeasure such as power off switch can be operated independently of the controller. Otherwise, it can result in damage to equipment and/or serious injury to personnel.

# Table of contents

| Chapter 1 | Introduction                                                                                                                           | 1-1 to 1-2  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

|           | 1.1 Before Use                                                                                                                         | 1- 1        |

|           | 1.2 Contents                                                                                                                           | 1- 2        |

|           | 1.2.1 Outline                                                                                                                          | 1- 2        |

|           | 1.2.2 Characteristics                                                                                                                  | 1- 2        |

|           | 1.3 Notes to Use                                                                                                                       | 1- 2        |

| Chapter 2 | Structure                                                                                                                              | 2-1 to 2-2  |

|           | 2.1 Structure and Parts name                                                                                                           | 2- 1        |

|           | 2.2 Module nameplate and Signals                                                                                                       | 2- 2        |

|           | 2.3 LED display                                                                                                                        | 2- 2        |

| Chapter 3 | Specifications                                                                                                                         | 3-1 to 3-2  |

| Chapter 4 | Interface                                                                                                                              | 4-1 to 4-4  |

|           | 4.1 Input Interface                                                                                                                    |             |

|           | 4.1.1 Example: Connection with differential Output                                                                                     |             |

|           | 4.1.2 Example: Connection with open Collector Output                                                                                   |             |

|           | 4.2 Output Interface                                                                                                                   |             |

|           | 4.2.1 Example: Connection with extend device                                                                                           |             |

|           | 4.3 How to Connect                                                                                                                     | 4- 3        |

| Chapter 5 | Setting                                                                                                                                | 5-1 to 5-3  |

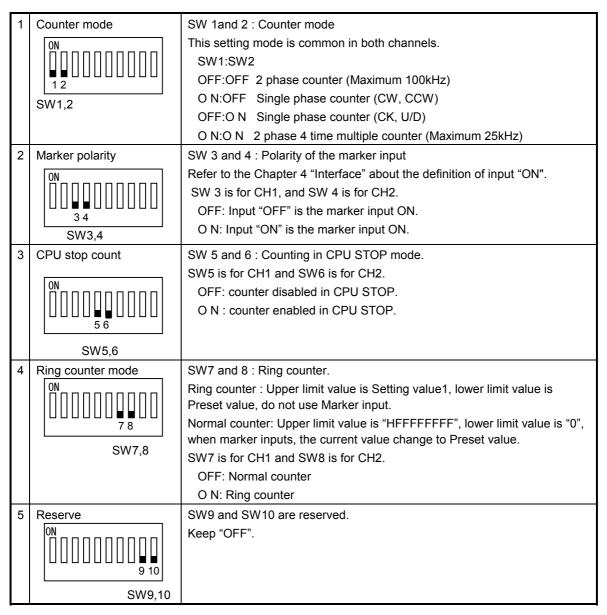

|           | 5.1 Setting dip - switches                                                                                                             | 5- 1        |

|           | 5.2 Counter specifications and setting items                                                                                           | 5- 2        |

| Chapter 6 | Installation and Wiring                                                                                                                | 6-1 to 6-2  |

|           | 6.1 Installation of Module                                                                                                             | 6- 1        |

|           | 6.2 Loading the Module                                                                                                                 | 6- 1        |

|           | 6.3 Wiring                                                                                                                             |             |

| Chapter 7 | Programming                                                                                                                            | 7-1 to 7-15 |

|           | 7.1 I/O Assignment                                                                                                                     | 7- 1        |

|           | 7.2 Input and Output registers                                                                                                         |             |

|           | 7.3 Detail of Registers                                                                                                                |             |

|           | 7.3.1 WXr u s 0 Status Register                                                                                                        | 7- 2        |

|           | 7.3.2 WY r u s 5 Control Register                                                                                                      | 7- 3        |

|           | 7.3.3 Communication Specifications Between EH-CPU and EH-CU                                                                            | 7- 4        |

|           | 7.4 Control command                                                                                                                    | 7- 5        |

|           | 7.4.1 Command list                                                                                                                     | 7- 5        |

|           | 7.5 Command specifications                                                                                                             | 7- 5        |

|           | 7.5.1 Global command                                                                                                                   | 7- 5        |

|           | 7.5.2 Setting command                                                                                                                  | 7- 6        |

|           | 7.5.3 Flag command                                                                                                                     | 7- 9        |

|           | 7.6 User Program                                                                                                                       | 7-11        |

|           |                                                                                                                                        | 7 1 1       |

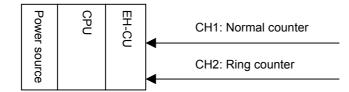

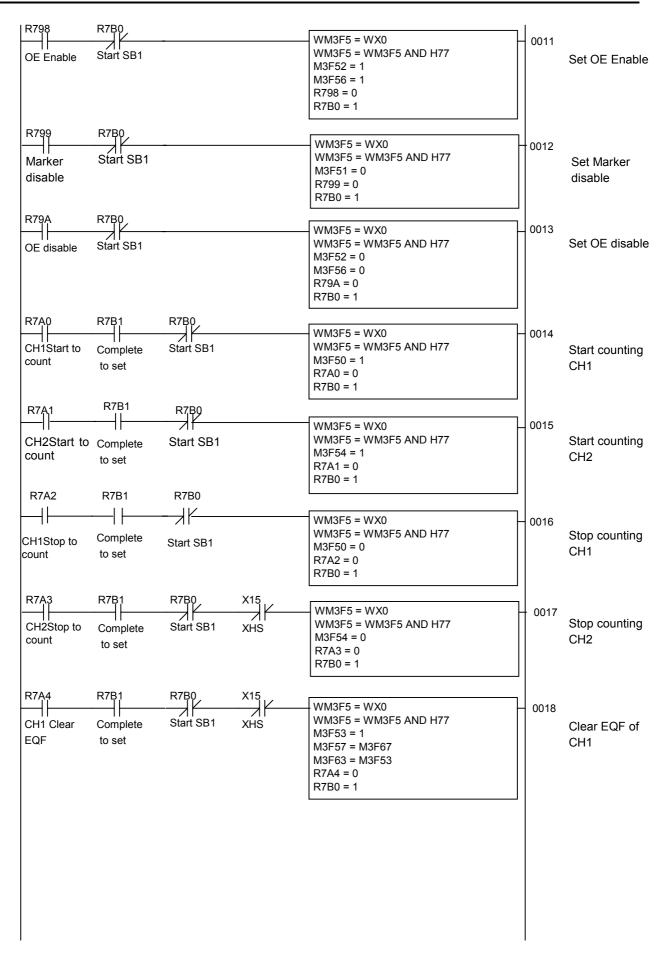

|           | <ul><li>7.6.1 Module construction about the next example of setting the counter</li><li>7.6.2 Example of setting the counter</li></ul> |             |

| Chapter 8 | Daily and Periodic Inspection | 8-1  |

|-----------|-------------------------------|------|

|           | 8.1 Daily Inspection          | 8- 1 |

|           | 8.2 Periodic Inspection       |      |

| Chapter 9 | Troubleshooting               | 9-1  |

| 1100 | loconocing                                      | 51   |

|------|-------------------------------------------------|------|

| 9.1  | When EH-CU does not count pulses                | 9- 1 |

|      | When the comparison output does not become "ON" |      |

# Chapter 1 Introduction

We appreciate that you have selected the EH-150 Counter Module of the Hitachi programmable logic controller. This application manual describes how to properly operate the EH-150 Counter Module(hereinafter called as the EH-CU/CUE). Read carefully this manual to familiarize yourself with the procedures respectively of installation , operation, and maintenance and check. The following documentation related to the EH-150 PLC is also available and should be used together.

| Item                         | Name of documentation                         | Manual No.      |

|------------------------------|-----------------------------------------------|-----------------|

| EH-150 APLLICATION<br>MANUAL | EH-150 Application Manual                     | NJI-280*X       |

| Programming Software         | LADDER EDITOR (MS-DOS version)                | NB-325*X        |

|                              | LADDER EDITOR for Windows®(Windows®95/98/NT4) | NJI-206*X/299*X |

| Counter module               | Counter module (EH-CU/CUE) Application Manual | NJI-321*X       |

| Table 1.1 | List of manual |

|-----------|----------------|

|-----------|----------------|

\*The last character of the manual number may be modified when the product is revised. Notes. The contents of this manual may be modified without previous notice.

#### 1.1 Before Use

When you purchased the EH-series Counter Module , please check the following matters:

- (1) If model name and specifications are correct.

- (2) If there is no shipping damage on product (If any, consult the dealer of the counter module.)

- (3) If following parts are in a carton box.

| No. | Products name               | Model number         | Outlook | Pcs | Remarks |

|-----|-----------------------------|----------------------|---------|-----|---------|

| 1   | EH-series Counter<br>Module | EH-CU or<br>EH-CUE   |         | 1   |         |

| 2   | Natao to upo                | NJI-322*: Japanese   | -       | 1   |         |

| 2   | Notes to use                | NJI-322*(X): English | -       | 1   |         |

Table 1.2 List of Counter Module Parts

### 1.2 Outline

### 1.2.1 Outline

- 1. EH-150 Counter Module (EH-CU/CUE) is a special function module that is installed on the basic base or expansion base of EH-150 series.

- 2. EH-CU/CUE can count high speed pulse train that digital input module cannot follow.

- 3. EH-CU/CUE can output according to the data set by user program.

#### 1.2.2 Characteristics

- 1. EH-CU/CUE is 1 slot module size, with 2 / 1 channels 32 bit counter.

- 2. EH-CU/CUE can count 4 mode pulse types which are 2 phase input mode, single phase (CW/ CCW signal) mode, 2 phase input mode (4 time multiplied) and single phase (Clock and direction signal) mode. These modes are selectable by dip setting switches.

- 3. High speed. (Maximum frequency is 100kHz (25kHz at 4 time multiplied mode).)

- 4. EH-CU/CUE has 2 types of interfaces. The one is differential input (line driver) and the other is open collector input (12-24 V DC).

- 5. EH-CU/CUE has ring counter mode too.

- 6. High speed response (less than 1ms) output. The comparison output is open collector type, so EH-CU/CUE can be connected to the external device directly.

- 7. In normal counting mode EH-CU/CUE can be set to the preset value from the current value by marker input.

- 8. EH-CU/CUE can memorize the current values at marker input (each channel 63 points). (Available from ROM version 0010 or later)

#### 1.3 Notes to use

- (1) EH-CPU5\*\*/448/3\*\*/\*\*\*A should be used with EH-CU/CUE. In case CPU is CPU104/208, CPU with ROM Rev.02 or later should be used. (But the external output of double words (DYrus5 to 6) can't be used.)

- (2) There are some limitations of comparison output and marker input. In details, refer to 5.2 "Normal counter and Ring counter".

- (3) When installing or uninstalling, turn off the power supply.

- (4) EH-CU/CUE is high-speed input module which can count max. 100 kHz. If there is a noise on input signal, EH-CU/CUE may count wrong. External cables of EH-CU/CUE should be laid out fully apart from the other power and signal cables. In detail refer 6.3 "Wiring".

- (5) When input frequency is higher, the input signal may be changed by wiring method, length of wiring, kind of cable, and driver spec. of pulse output. Use a differential output line driver as possible.

# Chapter 2 Structure

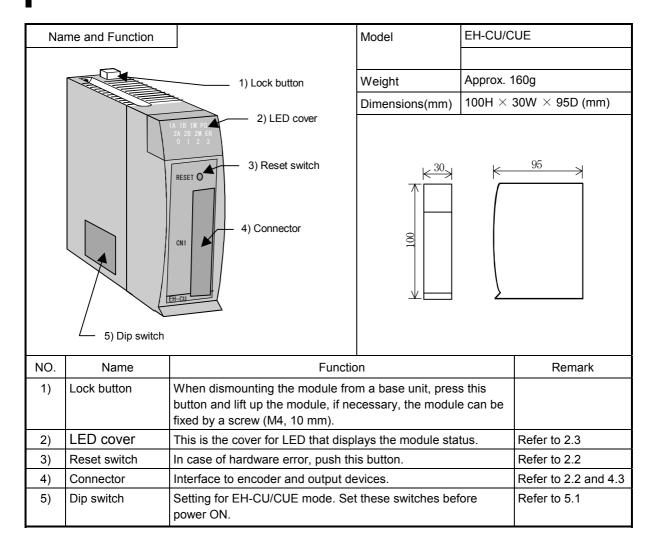

### 2.1 Structure and Parts name

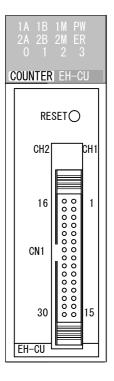

#### 2.2 Module nameplate and Signals

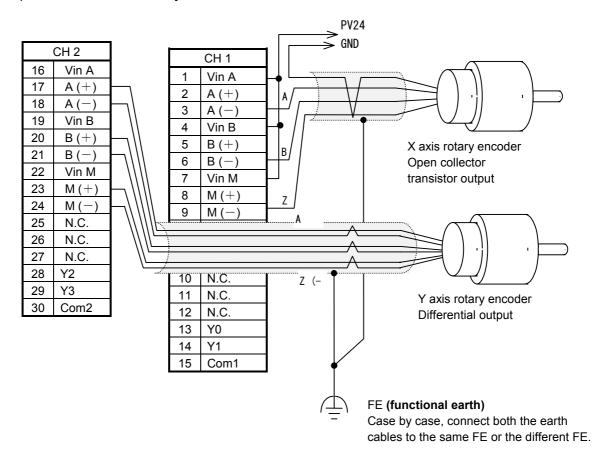

| No. | Ch. 2 | No. | Ch. 1 |                             | Voltage input<br>(Open collector)  | Differential input<br>(Line driver) |

|-----|-------|-----|-------|-----------------------------|------------------------------------|-------------------------------------|

| 16  | Vin A | 1   | Vin A | А                           | 12-24V power                       | NC                                  |

| 17  | A (+) | 2   | A (+) | ]                           | NC                                 | (+) signal                          |

| 18  | A (–) | 3   | A (–) |                             | Open collector                     | (-) signal                          |

| 19  | Vin B | 4   | Vin B | В                           | 12-24V power                       | NC                                  |

| 20  | B (+) | 5   | B (+) |                             | NC                                 | (+) signal                          |

| 21  | B (–) | 6   | B (–) |                             | Open collector                     | (-) signal                          |

| 22  | Vin M | 7   | Vin M | М                           | 12-24V power                       | NC                                  |

| 23  | M (+) | 8   | M (+) |                             | NC                                 | (+) signal                          |

| 24  | M (–) | 9   | M (–) |                             | Open collector                     | (-) signal                          |

| 25  |       | 10  |       |                             | NC                                 |                                     |

| 26  |       | 11  |       |                             |                                    |                                     |

| 27  |       | 12  |       |                             |                                    |                                     |

| 28  | Y2    | 13  | Y0    | Ŀ                           | Comparison output (Open collector) |                                     |

| 29  | Y3    | 14  | Y1    | output                      | Comparison output (Open collector) |                                     |

| 30  | Com 2 | 15  | Com 1 | 1 Com1 and 2 are separated. |                                    | arated.                             |

Note: The pin number defined of EH-CU/CUE is different from the number of the connector itself. CH2 is available in EH-CU only.

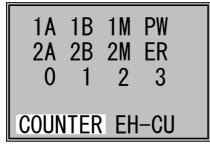

#### 2.3 LED display

| LED        | Meaning       | ON                                | OFF                               | Blinking                             |

|------------|---------------|-----------------------------------|-----------------------------------|--------------------------------------|

| PW         | Power LED     | Normal operation                  | Hardware error                    | Parameters setting is not completed. |

| ER         | Error LED     | Hardware error                    | Normal operation                  | -                                    |

| 1A         | Ch-1, A-phase |                                   |                                   |                                      |

| 1B         | Ch-1, B-phase |                                   | Corresponding input signal is OFF |                                      |

| 1M         | Ch-1, Marker  | Corresponding input               |                                   |                                      |

| 2A         | Ch-2, A-phase | signal is ON                      |                                   | -                                    |

| 2B         | Ch-2, B-phase |                                   |                                   |                                      |

| 2M         | Ch-2, Marker  |                                   |                                   |                                      |

| 0, 1, 2, 3 | Output Y0-Y3  | Corresponding output signal is ON | Corresponding input signal is OFF | -                                    |

Note 1 : Marker LED's 1M and 2M are independent from the marker polarity setting. These LED's light up when the input is "ON" . The meaning of "ON" is mentioned in the chapter 4.

Note 2 : Error LED lights up when the reset switch is pushed, but it is normal.

Note 3 : LED 2A,2B,2M, 2 and 3 are available in EH-CU only.

# Chapter 3 Specifications

# 3.1 General specifications

| Item                               | Specification                                                                                                                          |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operating temperature and humidity | 0 to 55 °C, 20 to 90 %RH (no condensation)                                                                                             |  |  |  |

| Storage temperature and humidity   | -10 to 75 °C, 10 to 90 %RH (no condensation)                                                                                           |  |  |  |

| Vibration resistance               | In accordance with JIS C 0911                                                                                                          |  |  |  |

| Noise resistance                   | ONoise voltage 1500 Vpp Noise pulse width 100 ns, 1 $\mu s$ by using noise simulator. ( According to Hitachi internal test procedure.) |  |  |  |

|                                    | OBased on NEMA ICS 3-304 (with the exception of input module)                                                                          |  |  |  |

|                                    | OStatic noise : 3000 V at metal exposed area                                                                                           |  |  |  |

| Dielectric withstand voltage       | 250 V DC between External signal terminal and case ground (FG) terminal                                                                |  |  |  |

| Current consumption                | 5 V DC 310 mA                                                                                                                          |  |  |  |

| Usage environment                  | No corrosive gasses, no excessive dirt                                                                                                 |  |  |  |

| Structure                          | Attaches to an open wall                                                                                                               |  |  |  |

| Cooling                            | Natural air cooling                                                                                                                    |  |  |  |

Table 3.1

General Specifications

### 3.2 General specifications

Table 3.2 Performance Specifications

| Item               |                 | Specifications                                                                                  |           |  |

|--------------------|-----------------|-------------------------------------------------------------------------------------------------|-----------|--|

|                    |                 | EH-CU                                                                                           | EH-CUE    |  |

| Count range        |                 | 32 bit (0 to 4 294 967 295)                                                                     |           |  |

| Countable pu       | lse frequency   | 100 kHz (25 kHz at 4 time multiple)                                                             |           |  |

| Count mode         |                 | 2 phases, single phase (CW/CCW,CK/U/D) and 2 phases 4 time multiple (Common for both channels.) |           |  |

| Number of ch       | annel           | 2 channels                                                                                      | 1 channel |  |

| Differential in    | out voltage     | 5V DC (Min. 4mA)                                                                                |           |  |

|                    | ON voltage      | Min. 2.0 V                                                                                      |           |  |

|                    | OFF voltage     | Max. 0.8 V                                                                                      |           |  |

| Open collecto      | r input voltage | 12 to 24 V DC                                                                                   |           |  |

|                    | ON voltage      | Min. 10 V                                                                                       |           |  |

|                    | OFF voltage     | Max. 4 V                                                                                        |           |  |

| Isolation syste    | em              | Photo-coupler isolation                                                                         |           |  |

| Phase              | A: A, CW, CK    |                                                                                                 |           |  |

| difference         | B: B, CCW, U/D  | + 45° to +125° at forward rotation<br>- 45° to - 125° at reverse rotation                       |           |  |

| (A-B)              | M: Marker (Z)   |                                                                                                 |           |  |

| Count pulse width  |                 | ON : 4 µs, OFF : 4 µs or more                                                                   |           |  |

| Marker pulse width |                 | 10 μs or more (ON edge)                                                                         |           |  |

| External conn      | ector           | 30-pin connector for 2 channels                                                                 |           |  |

| External wirin     | g               | Paired common shielded wire                                                                     |           |  |

|                               | lta      |                | Specif                                             | Specification                      |  |  |

|-------------------------------|----------|----------------|----------------------------------------------------|------------------------------------|--|--|

| Item                          |          | rn             | EH-CU EH-CUE                                       |                                    |  |  |

| Output voltage                |          |                | 12/24 V DC (maximum 30 V DC)                       |                                    |  |  |

| Load current                  |          |                | Maximum 20 mA/ point                               |                                    |  |  |

| Output m                      | ode      |                | Transistor ( open collector )                      |                                    |  |  |

| Minimum                       | load cu  | irrent         | 1 mA                                               |                                    |  |  |

| Output de                     | elay     | ON to OFF      | 1 ms or less                                       |                                    |  |  |

| time                          |          | OFF to ON      | 1 ms or less                                       |                                    |  |  |

| Voltage d                     | rop      |                | Maximum 1.5 V                                      |                                    |  |  |

| External of                   | output p | oints          | 4 points (selectable each channel)                 | 2 points (selectable each channel) |  |  |

|                               | Up an    | d down counter | Current value = (latch) comparison value 1 or      |                                    |  |  |

|                               |          |                | Current value > (level ) comparison value 1        |                                    |  |  |

|                               | Ring c   | counter        | Current value = (latch) comparison value 2         |                                    |  |  |

| Leak current                  |          |                | Maximum 0.5 mA                                     |                                    |  |  |

| Polarity                      |          |                | Minus (-) side in module (common) . Common is (-). |                                    |  |  |

| External power supply voltage |          |                | 12/24 V DC (Maximum 30 V DC)                       |                                    |  |  |

| Isolation                     | system   |                | Photo-coupler isolation                            |                                    |  |  |

| Table 3.3 | Output Specifications |

|-----------|-----------------------|

|-----------|-----------------------|

#### Table 3.4 Count method

|                                      | Count method                                   |                    | Selectable by Dip switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dip<br>switches |  |  |  |

|--------------------------------------|------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| 2 p<br>Mc                            | Up = A & B↑                                    | Phase A<br>Phase B |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SW1:OFF         |  |  |  |

| 2 phase<br>Mode 1                    | Down = A & B↓                                  | Phase A<br>Phase B |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SW2:OFF         |  |  |  |

| (CW/CCW)<br>single phase<br>Mode 2   | Up = A↓ & B<br>A = CW, B = CCW                 | Phase A<br>Phase B | Image: the second se | SW1:ON          |  |  |  |

| CCW)<br>phase<br>le 2                | Down = A & B↓<br>A = CW, B = CCW               | Phase A<br>Phase B |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |  |  |  |

| (CK/U/D)<br>single phase<br>Mode 3   | Up = B & A↓<br>A = CK, B = Up/Down             | Phase A<br>Phase B | (High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SW1:OFF         |  |  |  |

| J/D)<br>ohase<br>e 3                 | Down = B & A↓<br>A = CK, B = Up/ Down          | Phase A<br>Phase B | (Low)*1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SW2:ON          |  |  |  |

| 2 phase (4 ti<br>multiple)<br>Mode 4 | Up = A & B↑+ Ā & B↓<br>+ Ē & A↑ + B & A↓       | Phase A<br>Phase B |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SW1:ON          |  |  |  |

| (4 time<br>iple)<br>le 4             | Down = A & B↓<br>+ Ā & B↑ + B & A↑<br>+ Ē & A↓ | Phase A<br>Phase B |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SW2:ON          |  |  |  |

#### $\uparrow$ or $\downarrow$ is the counting timing.

\*1 High is input "OFF", Low is input "ON".

### 3.3 Counter value record mode (ROM ver. 0010 or later)

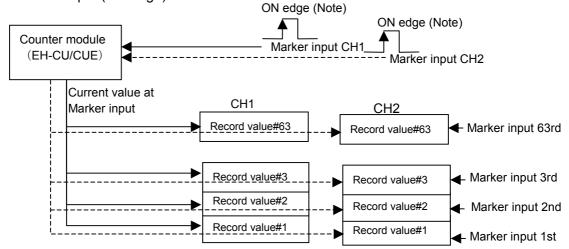

#### (1) Counter value record mode

EH-CU/CUE memorizes the current value to the internal memory of EH-CU/CUE at the rising edge of marker input (ON edge).

(Note) When DIP SW3/4 is "ON", timing is ON edge, when DIP SW is "OFF", timing is "OFF edge". CH2 is available in EH-CU only.

| Table 3.4 Count value record mode specification | ۱ |

|-------------------------------------------------|---|

|-------------------------------------------------|---|

| Item                             | Specification          | Remark                                    |

|----------------------------------|------------------------|-------------------------------------------|

| Maximum record number            | Each channel 63 points | Data after the 64th time is not recorded. |

| Record 2 channel<br>Simultaneous | Possible               |                                           |

| Maximum record frequency         | 50 kHz or less         | Error ±3 pulses                           |

#### (2) Record mode setting

Use a count value record mode setting command (see 7.5.4)

(3) Read the recorded data

Use a count record data read command (see 7.5.4).

- (4) Clear the recorded data Use a count record data clear command (see 7.5.4).

- (5) Read the record mode setting Use a count record value read command (see 7.5.4).

- (6) Execute record

#### Data is recorded only when marker is enable (ME1 and ME2 is "1").

(Note) When marker is disable, the following is possible to use. Record mode setting, Read the record data, Clear the record data, Read record mode setting.

(7) Power failure memory

EH-CU/CUE does not support power failure memory. When you need power failure memory, store the data to CPU memory which is set power failure memory by read the record data command.

#### (8) Operation of CPU RUN to STOP and STOP to RUN

Even when CPU operation is from RUN to STOP or from STOP to RUN, recorded data is not cleared.

# Chapter 4 Interface

### 4.1 Input Interface

#### < Input interface circuit >

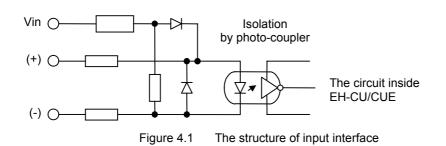

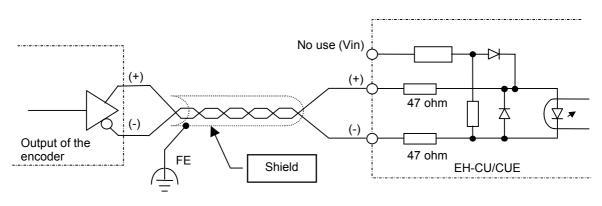

The input interface of EH-CU/CUE has both interfaces for differential output and for open collector output. Figure 4.1 shows the structure of the interface circuit. (Only one signal is shown)

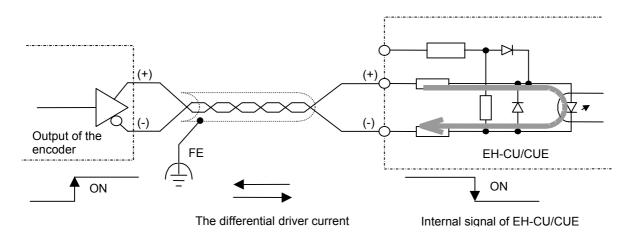

Figure 4.2 The interface with differential input

#### <Definition of input "ON">

When the differential driver current of the encoder passes the photo-coupler, input signal turns "ON" as below figure.

### 4.1.2 Example : Open collector output

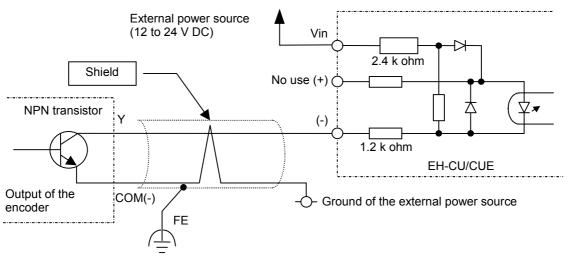

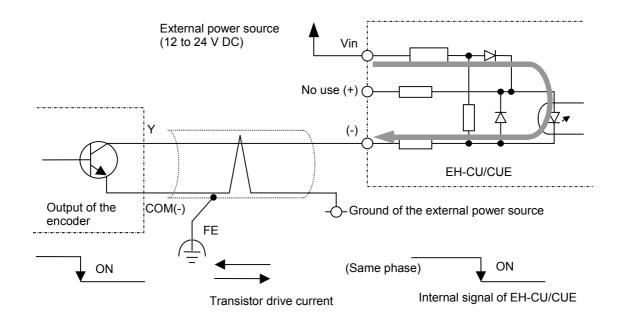

Figure 4.3 The interface with open collector output

<Definition of input "ON">

When the transistor current of the encoder run the photo-coupler, input signal is "ON" like under figure.

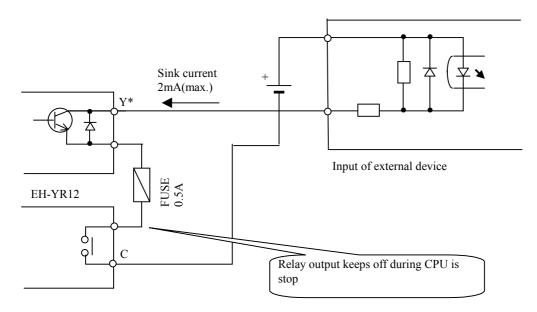

### 4.2 Output Interface

#### < Output interface circuit >

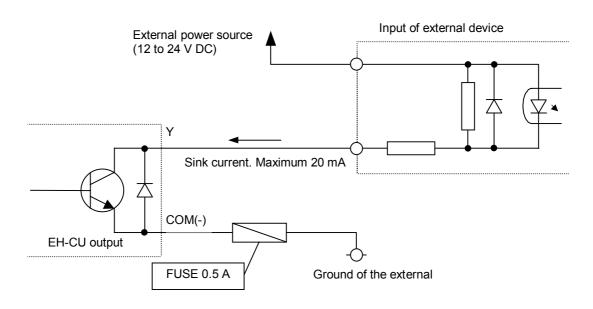

EH-CU/CUE has output interfaces of open collector type. Figure 4.4 shows a structure of the circuit. When the output transistor is "ON", the output current flows into the output transistor. Please connect an additional fuse rated about 0.5A to each COM terminal outside, for protection of internal wiring.

4.2.1 Example: Connection with external device

Figure 4.4 The interface of transistor

#### 4.3 How to connect

Use the connector specified as below or compatible one.

#### 1. Connector model for EH-CU/CUE side

HIF3BA-30PA-2.54DS 30pin (male connector) made by HIROSE or equal one.

#### 2. Connector model for the device side. Free wires and pin-socket of solderless type.

| Connector case                     | HIF3BA-30D-2.54C                | Connector case for 30 pins                       | Supplied by<br>HIROSE |

|------------------------------------|---------------------------------|--------------------------------------------------|-----------------------|

| Connector pin<br>(applicable tool) | HIF3-2226SCC<br>(HIF3-TB2226HC) | Partial plated terminal<br>For AWG#22-26 wire *1 | Supplied by<br>HIROSE |

| Connector case cover               | HIF3-30CV                       |                                                  | Supplied by<br>HIROSE |

\*1 AWG22-26 wire is \u00f60.64-0.40mm

Refer Chapter 6.3 "Wiring" about the notes of wiring.

Example: connection to a rotary encoder

Refer to Chapter 6.3 "Wiring" about the notes of wiring.

# Chapter 5 Setting

### 5.1 Setting dip switches

Set the dip switches by a certain sharp tool carefully, and do not touch other electric parts.

The other functions can be set by software commands. Refer to Chapter 7 about the detail of software commands.

# 5.2 Normal counter and Ring counter

|                      | Item                     | Normal counter                                                                      | Ring counter                                              |

|----------------------|--------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------|

|                      | Minimum value            | 0                                                                                   | Specified in Preset value *1                              |

|                      | Maximum value            | HFFFFFFF                                                                            | Specified in Setting value *1                             |

|                      | Over flow flag           | When the current value changes<br>HFFFFFFFF to 0, this flag will be "1".            | Not available                                             |

| Spe                  | Under flow flag          | When the current value changes 0 to HFFFFFFFF, this flag will be "1".               | Not available                                             |

| Specification        | Over flow flag clear     | When this flag is "1", the over flow flag will be cleared (level).                  | Not available                                             |

| on                   | Under flow flag clear    | When this flag is "1", the under flow flag will be cleared (level).                 | Not available                                             |

|                      | Count enable             | EH-CU starts counting when the enable bit is set "1".                               | EH-CU/CUE starts counting when the enable bit is set "1". |

|                      | Count disable            | EH-CU stops counting when the enable bit is set "0".                                | EH-CU/CUE stops counting when the enable bit is set "0".  |

|                      | Comparison               | In case of counting up,                                                             | In case of counting up,                                   |

|                      | (=, latch output)        | Comparison "=" means,                                                               | Comparison "=" means,                                     |

|                      |                          | (Counter) = (Setting value 1) + 1 *2                                                | (Counter) = (Setting value 1) + 1 *2                      |

|                      |                          | In case of counting down,                                                           | In case of counting down,                                 |

|                      |                          | Comparison "=" means,                                                               | Comparison "=" means,                                     |

| òm                   |                          | (Counter) = (Setting value 1) - 1 *2                                                | (Counter) = (Setting value 1) - 1 *2                      |

| Comparison detection | Comparison               | In case of counting up,                                                             | Not available                                             |

| isoi                 | (>, level output)        | Comparison ">" means,                                                               |                                                           |

| n de                 |                          | (Counter) > (Setting value 1) + 1 *2                                                |                                                           |

| tec                  |                          | In case of counting down,                                                           |                                                           |

| tion                 |                          | Comparison ">" means,                                                               |                                                           |

| _                    |                          | (Counter) > (Setting value 1) - 1 *2                                                |                                                           |

|                      | Comparison               | To clear Comparison "=" bit                                                         | To clear Comparison "=" bit                               |

|                      | (=, latch output) clear  |                                                                                     |                                                           |

|                      | Output enable or disable | For external output enabled or disabled                                             | For external output enabled or disabled                   |

| Z                    | Marker input             | When marker input is detected, the Current value is replaced by the Preset value *3 | Not available                                             |

| Marker               | Marker enable or disable | For marker input enabled or disabled.                                               | Not available                                             |

|                      | Marker logic             | For marker logic positive or negative.                                              | Not available                                             |

| S                    | Current value            | The current value *4                                                                | The current value of EH-CU/CUE *5                         |

| Setting value        | Preset value             | When marker input is detected, the Current value is replaced by the Preset value *4 | Used for the Minimum value *5                             |

| valu                 | Setting value 1          | Comparison value (Set point) *4                                                     | Used for the Maximum value *5                             |

| ē                    | Setting value 2          | Not available                                                                       | Comparison value (Set point) *5                           |

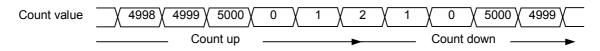

\*1 In case of Ring counter, the maximum value is included in the counted value.

Example) In case of the max. value is "5000", and min. value is "0".

| *2 | Definition of the of<br>In case of the co<br>In counting up, th                    | mparison (=, la                      | •           | ,         | n the c | current va | lue change | es "n" to '                   | 'n+1".    |    |

|----|------------------------------------------------------------------------------------|--------------------------------------|-------------|-----------|---------|------------|------------|-------------------------------|-----------|----|

|    | (n = Setting                                                                       | yvalue1)                             |             |           |         |            |            |                               |           |    |

|    | Count value                                                                        | n-2                                  | χ           | n-1       | χ       | n          | n+1        | χ                             | n+2       |    |

|    | Comparison or                                                                      | utput (=)                            |             |           |         | 4          | ON         |                               |           |    |

|    | In counting down<br>(n = Setting                                                   | n, the comparis<br>yvalue1 or Settir |             | is "ON" w | hen th  | e current  | value char | ıges "n" '                    | to "n-1". |    |

|    | Count value                                                                        |                                      | χ           | n+1       | χ       | n          | n-1        | χ                             | n-2       | _X |

|    | Comparison o                                                                       | utput (=)                            |             |           |         |            | ON         |                               |           |    |

|    | In case of the co<br>The comparison<br>(n = Setting<br>Count value<br>Comparison o | output is "ON"<br>value1)            |             | ,         | alue ch |            |            | or "n-1".<br>n-1 <u>/ n</u> - | -2        |    |

| *3 | Specification of t                                                                 | he marker inpu                       | ıt.(P= Pres | et value) |         |            |            |                               |           |    |

|    | Count value                                                                        | n r                                  | n+1 / n+2   | ХР        | ) P+1   | P+2        | (P+3 / F   | P+4 Y P                       | +5        |    |

|    | Marker input                                                                       |                                      |             | ♦ ON      |         |            |            |                               |           |    |

The marker input is detected at "ON" edge. So the counter keeps operation even if the marker is still "ON".

- \*4 In case of Normal counter mode, Current value, Preset value and Setting value 1 can be written during counting.

- \*5 In case of Ring counter mode, Current value can be written during counting, but the Current value should be between the min. and the max. value. The Preset value and Setting value1, 2 can be written only when CPU is in STOP mode. If these parameters are out of range or wrong combinations, PW LED will be blinking.

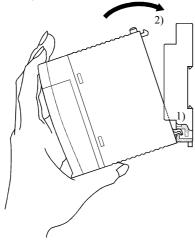

# Chapter 6 Installation and Wiring

### 6.1 Installation of Module

EH-150 can be installed in both the basic and expansion base unit. Install and uninstall the module after turn off the base unit power source. Set dip switch before installing the module according to Chapter 5.1 "Setting dip-switches".

### 6.2 Loading the Module

#### (1) Installing

- Hook the claw at the lower section of the module to the hole in the base.

- Press in the upper side of the module until it clicks.

- Note 1: After loading the module, check to make sure it does not come out.

- Note 2: Load the power module at the leftmost side of the base unit.

- Note 3: Load the CPU module and I/O controller to the right neighbor of the power module.

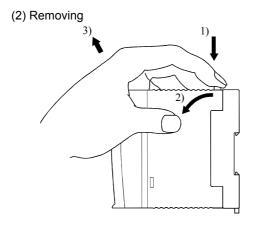

- 1) Push in the lock button.

- 2) With the lock button pushed in, pull the top of the module toward the front.

- 3) Raise it toward the top and pull it out.

- Note: For the power module, pull it out while pushing down the two lock buttons.

### 6.3 Wiring

Take much care of separation from the other wires. Because EH-CU/CUE that can count high frequency pulse that is maximum 100kHz is very sensitive to short width pulses, so in the case that the noise from the other wires come across to EH-CU/CUE, EH-CU/CUE may not count correctly. In case of high frequency, EH-CU/CUE may not count correctly by the wiring method, the length of wire, the

cable impedance or short of pulse drive power. So we recommend the differential input.

#### <Notes of wiring>

#### 1) Length of wire

Wire within 10m from EH-CU/CUE to the pulse output device like encoder.

2) Separation to the power lines.

Use the cable with shields for wiring to the pulse output device like encoder. In this case connect a drain wire to the shield net both sides, because it can be connected to the functional earth not only on the device side but also PLC side.

Separate the duct within the signal wires of EH-CU/CUE from other wires. (Another input/ output wires and power source wires)

3) Add a ferrite core

Insert a ferrite core with the input/output shielded wires, and wind the shielded wires by one turn around the ferrite core.

#### 4) Regarding failsafe

Construct an interlock circuit outside the PLC.

When PLC supply is turned on or off, the lag tome and difference in startup time between the PLC unit power and the external power (particularly DC power supply) for the PLC I/O module signals, may temporarily cause the I/O not to operate normally.

#### 5) Install a lightning arrestor

To prevent damage to equipment from being struck by lightning, it is recommended that a lightning arrestor is to be set up for each PLC power supply.

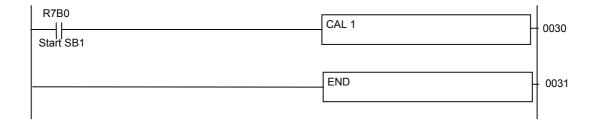

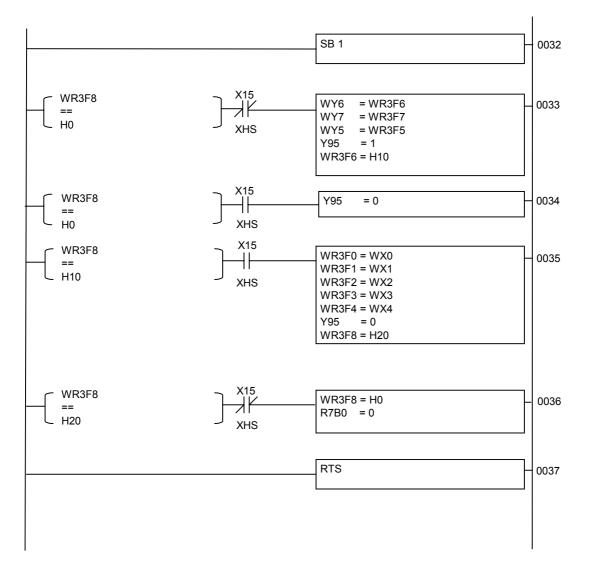

# Chapter 7 Programming

### 7.1 I/O Assignment

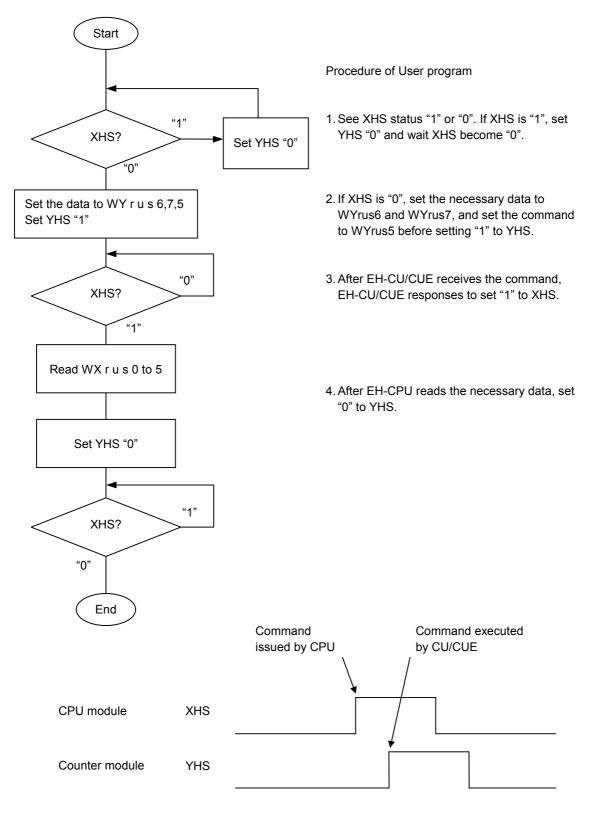

EH-CU/CUE occupies 8 words (5 words input (WX) and 3 words output (WY) ) I/O assignment is "  ${\bf FUN}~{\bf 0}$ ".

### 7.2 Input and Output register

The input and output registers of EH-CU/CUE are defined as the following table.

| Register NO.             | Direction                                          | Function                                                                                                                                                                                                                                                                      |

|--------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WXrus0                   | EH-CPU€EH-CU/CUE<br>(Reading from<br>EH-CU/CUE)    | Status Register<br>The information of EH-CU/CUE status can be monitored here.<br>The meaning of each bit depends on the command in the<br>Control Register.                                                                                                                   |

| WXrus1<br>WXrus2         | EH-CPU ← EH-CU/CUE<br>(Reading from<br>EH-CU/CUE)  | CH1 Status word (low word)*1<br>CH1 Status word (high word)*1<br>In normal operation (XHS=0), <b>the current value is set in this</b><br><b>register.</b> If XHS is "1", preset value or Setting value1 or 2 of<br>CH1, etc are set according to command in Control Register. |

| WX r u s 3<br>WX r u s 4 | EH-CPU 	← EH-CU/CUE<br>(Reading<br>from EH-CU/CUE) | CH2 Status word (low word)*1<br>CH2 Status word (high word)*1<br>In normal operation (XHS=0), <b>the current value is set in this</b><br><b>register.</b> If XHS is "1", preset value or Setting value1 or 2 of<br>CH2, etc are set according to command in Control Register. |

| WYrus5                   | EH-CPU→EH-CU/CUE<br>(Writing to<br>EH-CU/CUE)      | Control Register<br>Set command and handshake bit in this register in order to<br>control EH-CU/CUE.<br>Before the setting , Data words must be set in WYrus6, 7 in<br>advance.                                                                                               |

| WYrus6<br>WYrus7         | EH-CPU→EH-CU/CUE<br>(Writing to<br>EH-CU/CUE)      | Data word (low word)<br>Data word (high word)                                                                                                                                                                                                                                 |

Table 7.1 Function of the input and output registers

Note: r : Remote master number. (In the case of the module installed CPU unit, r= 0) u : unit or Remote slave station number.

- s : slot number on the base unit.

- 0 to 7: word number of the module.

- \*1 When CPU reads Status words (WX r u s 1 to 4), CPU can read the unit per word (16 bits) data correctly, but CPU can not read two words (32 bits) at the same time. In order to read the current value (32 bits) correctly, CPU should be set "Current value latch command" to Control Register and latch the count data before read the count data.

During handshake operation, the count value is fixed but the pulse counting is continued.

# 7.3 Detail of Registers

### 7.3.1 WX r u s 0 Status Register

The status of EH-CU/CUE is set in Status Register.

|            |     | WXrus0                                                         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|------------|-----|----------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit        | X15 | 15 X14 X13 X12 X11 X10 X09 X08 X07 X06 X05 X04 X03 X02 X01 X00 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Definition | XHS | -                                                              | CH2 | CH1 | OF2 | UF2 | OF1 | UF1 | EQ2 | OE2 | ME2 | CE2 | EQ1 | OE1 | ME1 | CE1 |

| Bit | Definition | Contents                                                                                                                                                                                                                             |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|